The Challenge

Current electronics are too energy-hungry to handle the requirements of AI workloads on edge devices, which have limited energy and area budgets in comparison to more powerful cloud systems. This is closing the door to important applications across industries such as ICT, mobility, healthcare, agri-food, industrial automation, and security, leaving an enormous untapped potential behind.

The Innovation

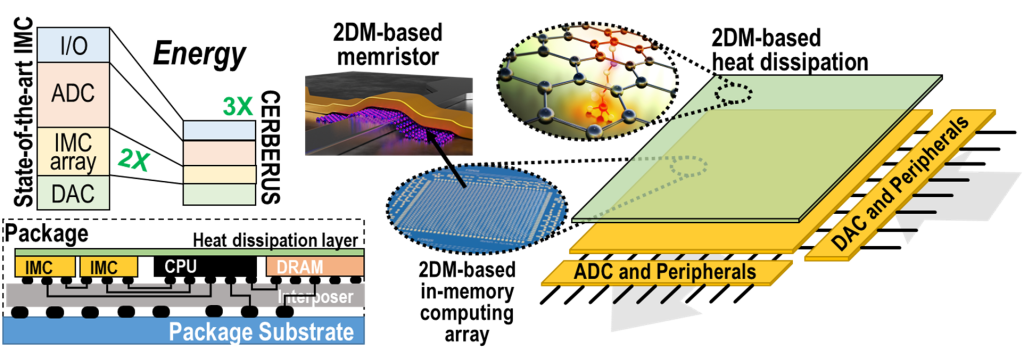

In-memory computing (IMC) and the associated non–von Neumann architectures are widely regarded as a way to dramatically improve the efficiency of AI processing, but their full potential is presently constrained by non-idealities within and around the IMC tiles. CERBERUS’s goal is to demonstrate a viable approach to overcoming the key limitations of current IMC architectures, reaching 3X better energy efficiency at the system level for modern and emerging edge AI computing workloads. This will allow powerful AI models to run on even the smallest edge devices.

The Approach

CERBERUS employs a three-pillar approach grounded on:

- 2× more efficient memristive devices,

- 30% more efficient peripheral circuits also allowing to bypass domain conversions,

- 70% more effective heat dissipation devices to virtually eliminate thermal noise

The Science

CERBERUS leverages 2D materials (2DMs)—in particular MoS₂, h-BN, and graphene—to develop innovative beyond-CMOS solutions with exceptional energy efficiency.

The project introduces several key innovations.

First, it experimentally validates energy-efficient in-memory computing (IMC) tiles based on 2DMs, demonstrating both their feasibility and their integration at the technological and architectural levels. Second, it develops a highly efficient graphene-based heat spreader to significantly reduce thermal noise during device operation. Third, it designs ultra-efficient peripheral circuits to effectively interface with the IMC tiles.

Finally, to maximize system-level efficiency, CERBERUS adopts a co-design approach that brings together hardware architectures and AI algorithms. This ensures that efficiency gains achieved at the device level are preserved, by optimally mapping workloads and developing AI models that align with the intrinsic physical properties of IMC systems.

Why It Matters

Since the slowdown of Moore’s Law, the semiconductor industry has been seeking new ways to improve the performance and efficiency of computing systems. In this context, in-memory computing (IMC) and the resulting non–von Neumann architectures offer a promising path toward extremely low power consumption for the core operations that underpin AI algorithms

CERBERUS aims to demonstrate a viable approach to overcoming the key limitations of current IMC architectures. By doing so, it paves the way for deploying advanced AI models across a wide range of devices—even in highly resource-constrained, extreme-edge environments.